# **Heterogeneous Integration Roadmap**

**Richard Rao (Marvell Technology)**

CMSE 2024 May 1st, 2024

# The Technology Roadmap Creating a Common Vision and Collaboration

The National Technology Roadmap for Semiconductors (NTRS) was initiated by SIA Technology Committee chaired by **Dr Gordon Moore**. He invited 179 technologists to a workshop in Irving Texas to create a common vision and collaboration of semiconductor technology over the next 15 years across industry, suppliers, customers, academia, government & national laboratories.. The report published in 1993 constitute the first open-source Semiconductor Technology Roadmap.

In 1998 the NTRS roadmap work was joined by four other regional Semiconductor Industry Associations: Taiwan, South Korea, Japan and Europe to become International Technology Roadmap for Semiconductors (ITRS), In 2014 decision was made by SIA to end ITRS. The last edition of ITRS was published July 8, 2016.

The Heterogeneous Integration team in ITRS in 2014 learnt of the closure of ITRS decided to continue the Technology Roadmap effort towards shared vision and collaboration for the next era of Moore's Law progress for Electronics Resurgence into the Future Decades.

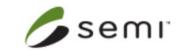

# The Definition of Heterogeneous Integration

semi

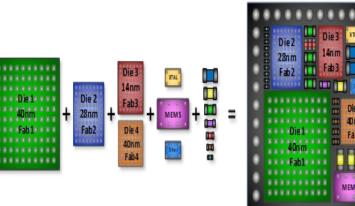

Die + Heterogeneous

System in Package (SiP)

#### Heterogeneous by multi-scale and multiphysics:

- Material

- Component type (IC, Photonics, MEMS, sensors)

- Circuit type (DRAM, Serdes, logic, RF, Power)

- Si Node

- Level/method of bonding/interconnection

#### Source: 2020 ISSC

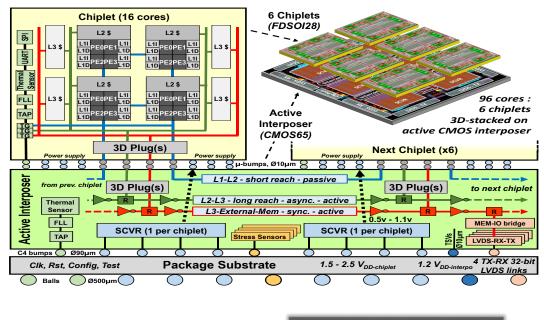

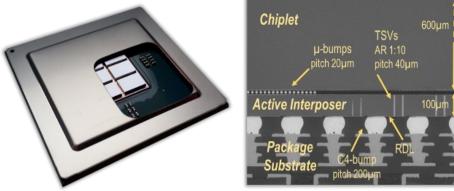

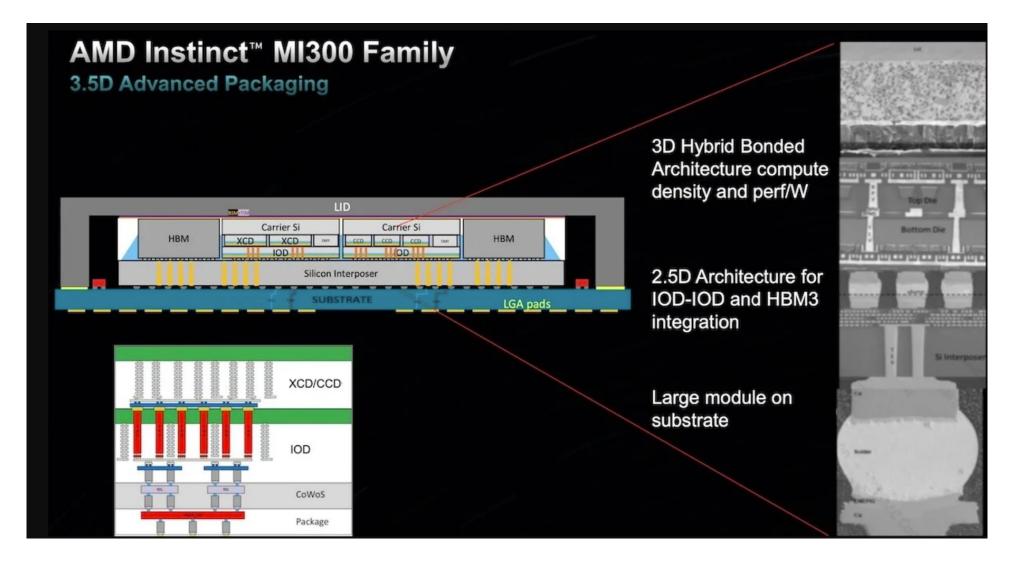

### AMD 3.5D Advanced Packaging

Society

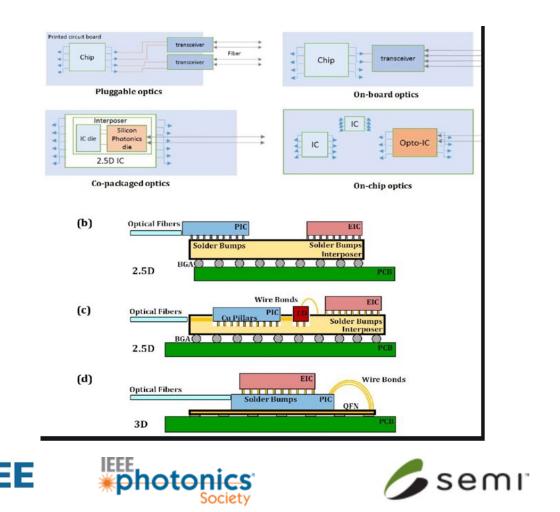

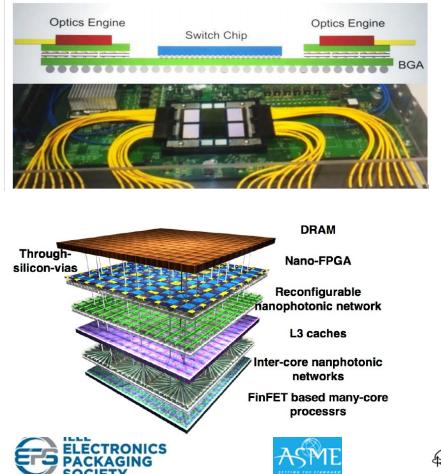

### **Heterogenous Integration of Electronics and Photonics**

#### Evolution of Photonics Packaging

Heterogenous integration of passive/active photonics devices and IC devices from board level to package and wafer levels

Co-Packaged Optics (CPO) Using 2.5D and 3D Packaging technology

ECTRON

# Heterogeneous Integration Roadmap (HIR)

### 23 Chapters Covering total Microelectronics Systems & Technology Ecosystem

### HI Systems & Market Applications

- High Performance Computing & Data Center

- Mobile

- Medical, Health & Wearables

- Automotive

- IoT

- Aerospace & Defense

### **Heterogeneous Integration Components**

- Single Chip and Multi Chip Integration (including Substrates)

- Integrated Photonics

- Integrated Power Electronics

- MEMS & Sensor integration

- 5G Communication & Beyond

### **Cross Cutting topics**

- Materials & Emerging Research Materials

- Emerging Research Devices

- Test

- Supply Chain

- Security

- Thermal Management

- Reliability

### **Integration Processes**

- SiP & Module

- 3D +2D & Interconnect

- Wafer Level Packaging (fan in and fan out)

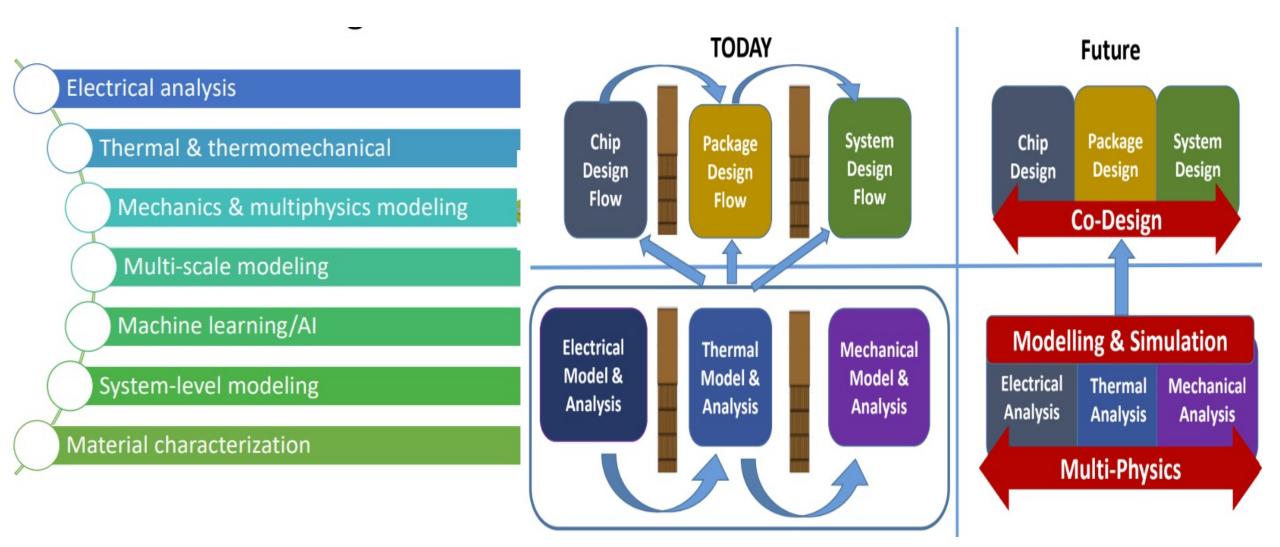

### **Co-Design** + Simulation

- Co-Design

- Modeling & Simulation

White Papers Stage: Additive Manufacturing and Quantum

### Hardware Reliability Topic Matrix

#### **Reliability road-map of HI systems requires coordination across all TWGs**

|                        | Reliability<br>Targets | Life Cycle<br>Conditions                     | Design for<br>Reliability                                  | Manufacturing for<br>Reliability                                                                      | KBT <sup>4</sup> for Reliability<br>Qualification:<br>EV/DV/PV <sup>1</sup> | PHM⁵            | Supply<br>Chain     |

|------------------------|------------------------|----------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----------------|---------------------|

| SiP<br>Technologies    | Photonic               | M/MCM ,<br>s, MEMS,<br>F/Analog              | TWGs:<br>Electromigration;<br>Materials; Co-<br>Design and | TWGs: SCM/MCM;<br>Photonics;<br>MEMS/Sensors; Power;<br>RF/Analog; Test                               |                                                                             | Security<br>TWG | Supply<br>Chain TWG |

| Package<br>Integration | Interconnec            | P, 2.5D/3D,<br>ts, SIP Topic<br>T; Substrate | Simulation Topic<br>Teams: Electrical                      | TWGs: WLP; 2.5D/3D;<br>Interconnects; SIP, Test;<br>Topic Teams: WST;<br>Substrate; Board<br>Assembly | Test TWG                                                                    |                 |                     |

| Applications           | MHW, Au                | obile, IoT,<br>Itomotive,<br>Prospace        |                                                            | TWGs: Mobile; IoT;<br>MHW; Automotive; HPC;<br>Aerospace; Test                                        |                                                                             |                 |                     |

| EE 👬 🎘                 | hotonic                | S'                                           | />semi                                                     | ELECTRON<br>PACKAGIN<br>SOCIETY                                                                       |                                                                             |                 | A Device Social     |

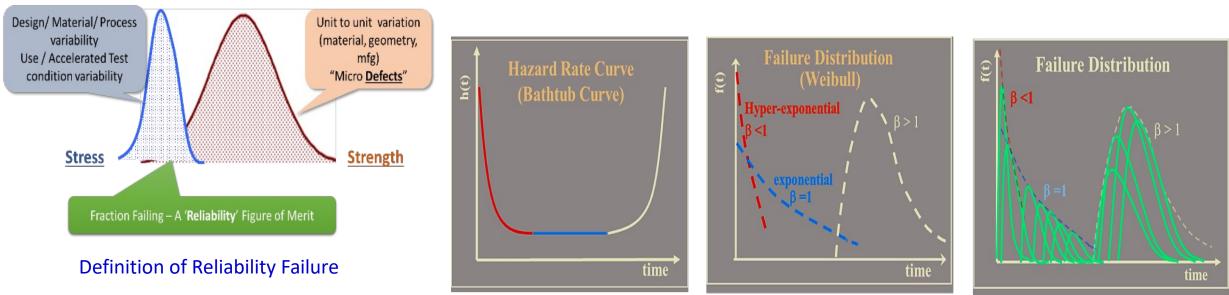

# **Heterogenous Integration System Reliability Introduction**

Systems with heterogeneous integration (HI) will experience new multiscale chippackage interactions and multi-physics failure modes

Managing reliability of HI systems will require holistic cradle-to-grave methodology

#### □ HI system reliability depends on aggregation of multiple degradation modes

In this era of Chiplets and multi-devices packages, innovations and collaborations in Reliability Technology and Science will be crucial for the semiconductor and microelectronics industries decades into the future.

Typical Bathtub Curve

based on hazard rates

System-level Bathtub Curve expressed as Weibull Failure Distribution

HI Systems Bathtub curve is the result of Multiple Competing Failure Modes

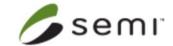

# **Reliability Methodology of HI Systems**

'Digital Twins' for managing reliability will rely on fusion methods that combine bottom-up physics and top-down big-data approaches

### **Reliability Challenges: Future Outlook**

|                     |                                                                                                                                                                                                                                                                     | Reliability<br>Targets                                                                                                                                                                                                                                                                    | Life Cycle<br>Conditions       | Design for<br>Reliability                        | Manufacturing for<br>Reliability | Qualification for<br>Reliability | Sustainment for<br>Reliability | Supply<br>Chain |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------------------|----------------------------------|----------------------------------|--------------------------------|-----------------|--|--|--|--|

| Applications        | Mobile<br>IoT<br>Medical, Health and wearables<br>Automotive<br>HPC & Data Centers<br>Aerospace and Defense                                                                                                                                                         | <ul> <li><u>1-5 Years</u>:</li> <li>Multi-physics fusion approaches for reliability assurance</li> <li>Bottom-up <i>Reliability Physics</i> based approaches, tools, infrastructure</li> <li>Top-down <i>Machine Learning &amp; AI</i> based approaches, tools, infrastructure</li> </ul> |                                |                                                  |                                  |                                  |                                |                 |  |  |  |  |

| Package Integration | WLP (FO/FI)<br>2.5D and 3D integration<br>Wafer Singulation and Thinning<br>Chip-package interactions (CPI)<br>Interconnects (TSV8s, µbumps,<br>wirebonds, Flip Chip solder joints)<br>Substrates/Interposers<br>Board Assembly<br>SOC/SIP/SOP <sup>9</sup> formats | <u>5-10 Yo</u><br>Fusio<br>next<br>• F                                                                                                                                                                                                                                                    | ears:<br>on appro-<br>gen robi | aches for co-c<br>ust HI systems<br>rant systems | lesign (based on '               |                                  |                                |                 |  |  |  |  |

| Technologies        | Microelectronics > 10 nm<br>Microelectronics > 10 nm<br>Photonics & optics<br>MEMS and sensors<br>Power electronics<br>Energy souces (Batteries/PV <sup>6</sup> /FC <sup>7</sup> )<br>RF/Analog Devices                                                             | 10 nm<br>10 nm<br>tics<br>sors<br>iss<br>s/PV <sup>6</sup> /FC <sup>7</sup> )<br>10 nm<br>Fusion approaches for intelligent, adaptive, reconfigurable products with<br>integrated autonomous life-cycle management capability<br>• Intelligent, self-cognizant systems                    |                                |                                                  |                                  |                                  |                                |                 |  |  |  |  |

# **Advanced Thermal Technologies & Research**

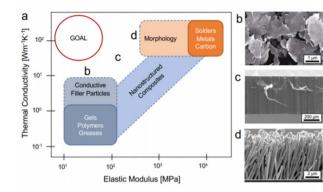

Figure 17 (a) Two common strategies can be employed to create high-performance TIM composites [14], (b) an example of graphene-polymer composite [15], (c) vertically grown nanotubes [16-17], (d) vertically electrodeposited nanowires [14, 18]

#### [A] Thermal Interface Materials

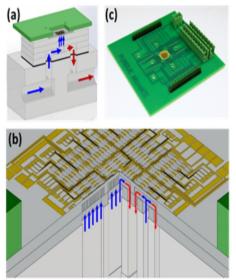

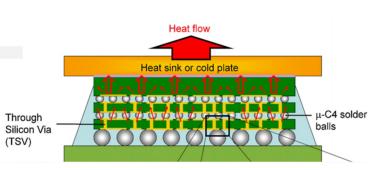

[C] Embedded liquid cooling of chip and chip stacks [B] System thermal limits for HPC multi-chip modules

A 3D chip stack using advanced materials in the conduction heat flow path.

#### [D] Advanced Thermal Materials for Thermal Management

TIM or

Air cooled heat sinks

Vapor Chambers

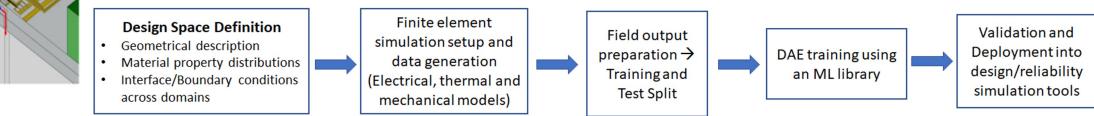

#### [E] Thermomechanical Modeling for Heterogeneous Integration

### **Modelling and Simulation Techniques**

**Co-Design Contents**

- Components of Co-Design

- Placement & routing, architecture

- Electromagnetics and electrical

- >Thermal management

- >Intelligent materials

- **>** Test

- Reliability, testing, mechanical

- Infrastructure and Research Needs

- University research (funding, workforce,...)

- Shared resources (open source, standards,...)

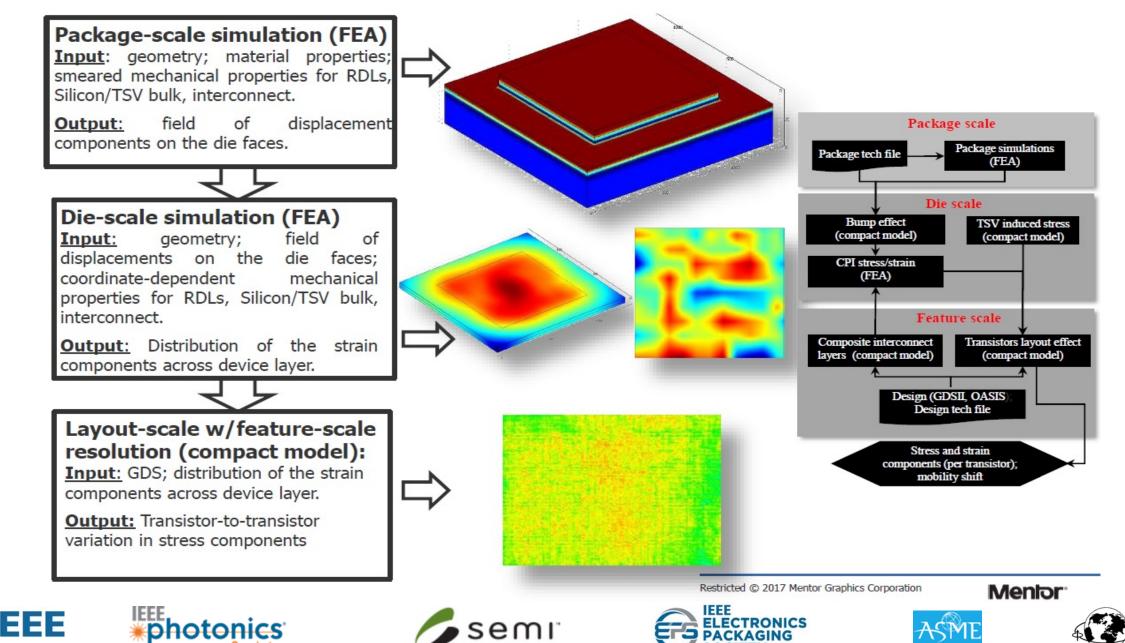

### **Multi-Scale and Multi-Physics CPI Flow**

OCIETY

LECTRON

SOCIETY

### "For while we have our eyes on the future, history has its eyes on us" Amanda Gorman, Poet Laureate